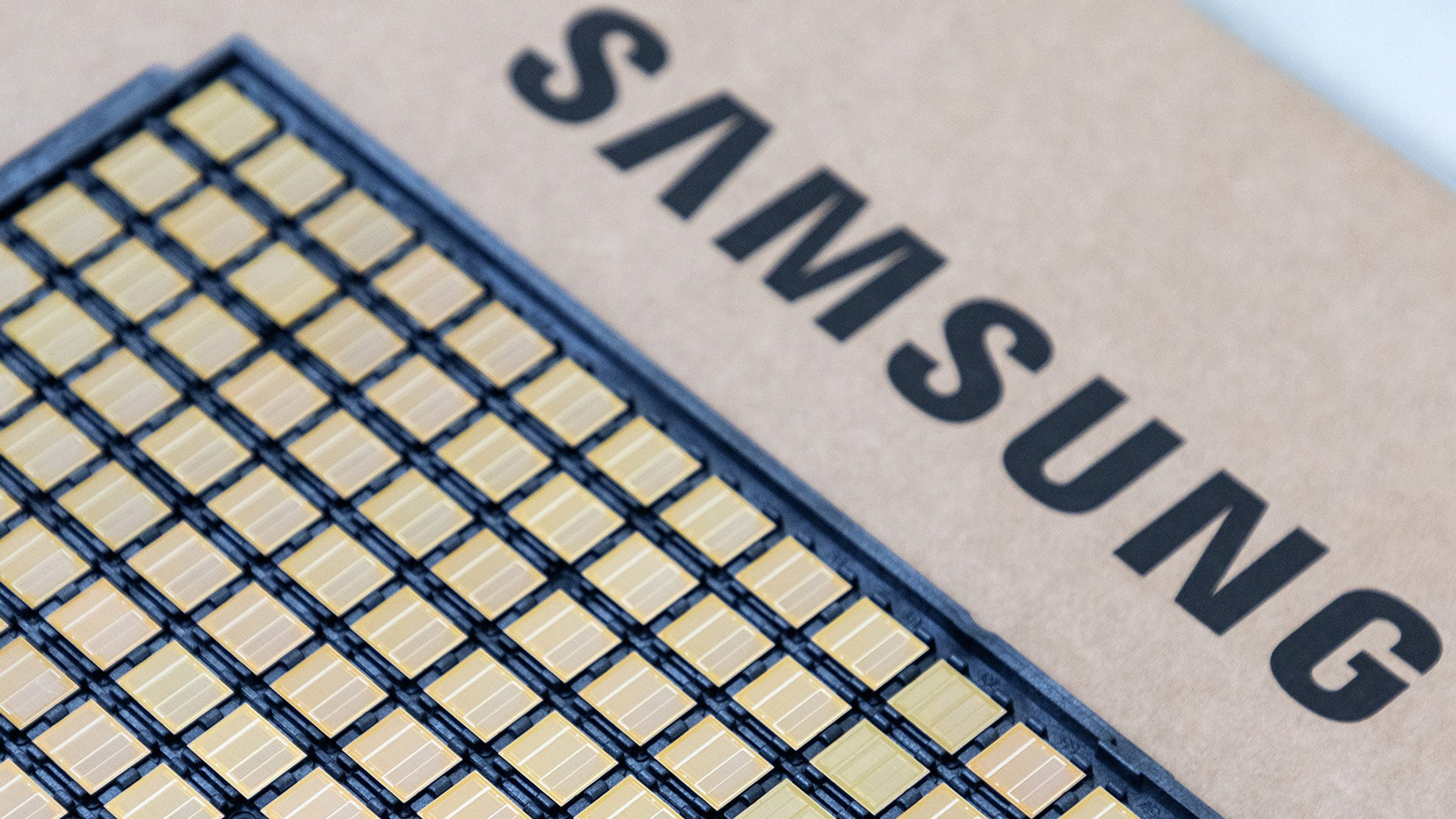

Samsung Explores a NAND Style Route for Future DRAM While SK hynix Pushes 4F² Vertical Gate Design in the Race for AI Memory Leadership

The next major DRAM battleground is starting to come into focus, and Samsung and SK hynix appear to be taking very different routes toward it. Recent industry reporting indicates that Samsung is evaluating a structure that borrows ideas from NAND manufacturing, while SK hynix is continuing to advance a 4F² vertical gate based approach as both companies look for a viable path beyond conventional DRAM scaling. The shift comes as AI server demand keeps pressure on HBM and advanced DRAM supply, forcing memory makers to think beyond the traditional planar roadmap.

At the center of the issue is a basic physical challenge. DRAM cells still rely on both a transistor and a capacitor, and shrinking them further becomes much harder when the capacitor must remain large enough to reliably store charge. That is why the industry has been increasingly focused on 3D DRAM concepts and 4F² class structures, which are seen as possible ways to keep boosting density and performance without simply squeezing existing layouts harder.

Samsung’s reported direction is especially interesting because it appears to borrow from a NAND style logic placement strategy. According to recent coverage citing industry sources, Samsung is considering a future DRAM architecture that combines a gate all around style transistor with a capacitor inside the DRAM cell, while also exploring the idea of placing support circuitry under the memory array, similar to how peripheral logic is handled in some modern NAND designs. That does not mean Samsung is literally turning DRAM into NAND, but it does suggest the company is looking across memory categories for manufacturing ideas that could unlock the next density step.

SK hynix, meanwhile, appears to be leaning harder into a 4F² vertical gate approach. Reporting from 2025 and 2026 has pointed to the company’s work on a structure that shrinks the cell footprint from the conventional 6F layout toward 4F while replacing planar transistor gates with vertically structured designs that wrap around the channel. The same direction is reflected in VLSI 2026 materials, which specifically reference SK hynix presenting electrical characteristics for 4F² vertical gate DRAM.

What makes this more interesting is that Samsung itself has also publicly shown 4F² related research. Reporting on ISSCC 2026 says Samsung presented a 4F² DRAM concept that combines a vertical channel transistor with wafer to wafer hybrid copper bonding. That suggests the real competitive picture is not simply Samsung on one side and SK hynix on another with completely unrelated ideas. Both appear to be chasing denser next generation DRAM structures, but with different priorities in how they get there and how much they are willing to borrow from adjacent technologies such as NAND style array to logic integration.

From a market standpoint, the timing is no coincidence. AI demand has already tightened supply across HBM and other advanced memory products, and recent reporting says Samsung and SK hynix have both warned that shortages could last through 2027 or longer as customers reserve supply years ahead. In that environment, the company that defines a scalable post planar DRAM architecture could gain a major advantage not only in commodity DRAM, but also in the higher margin AI memory segments that now shape the entire industry.

The most important thing to keep in mind is that these are still emerging directions rather than finished mass production products. The engineering challenge is enormous, and there is no guarantee that the first promising structure on paper becomes the winning commercial standard. But the broad message is clear: the old DRAM playbook is reaching its limits, and the next era may be decided by whichever company best combines transistor design, capacitor integration, bonding technology, and manufacturability at scale. Right now, Samsung appears willing to adapt a NAND inspired structural trick, while SK hynix is betting that a refined vertical gate path can carry it forward.

For the AI memory war, that is the real story. It is no longer just about who ships more HBM this quarter. It is about who defines what comes after today’s DRAM scaling wall.

Do you think Samsung’s cross over NAND style thinking or SK hynix’s 4F² vertical gate strategy has the stronger chance of becoming the foundation for next generation AI memory?