TSMC A16 Targets Up to 10% More Speed or 20% Lower Power Than N2P as Super Power Rail Moves Toward Q4 2026 Production

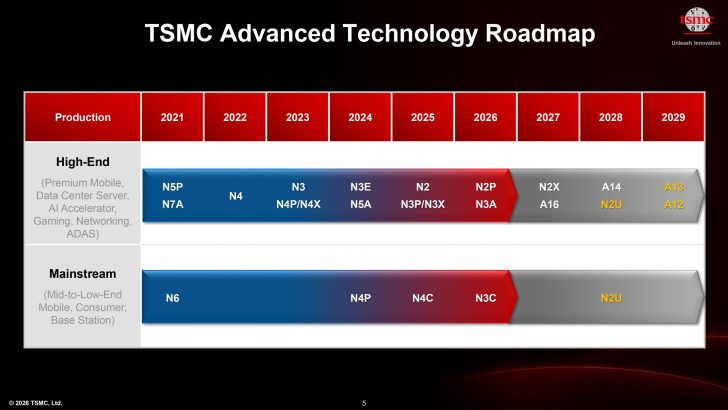

TSMC is using the upcoming VLSI symposium to put fresh focus on A16, its next major logic node for AI and high performance computing. The company’s preview positions A16 as an Angstrom class technology built around enhanced nanosheet transistors and its new backside power delivery approach, which TSMC brands as Super Power Rail. According to the VLSI 2026 technical preview and TSMC’s official A16 technology page, the node is aimed squarely at designs that need denser power delivery and more aggressive routing efficiency than the regular 2nm path can offer.

News from @TWSemicon at @VLSI_2026

— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) April 29, 2026

Paper T1.5

TSMC will present their A16 technology

➡️ A16 is N2P with backside power delivery

➡️ TSMC calls BSPDN 'Super Power Rail'

➡️ +8-10% perf or +15-20% power saving

➡️ Up to +8-10% chip density (logic + SRAM)

➡️ Mass production in 26Q4… pic.twitter.com/gD4ujvu0QC

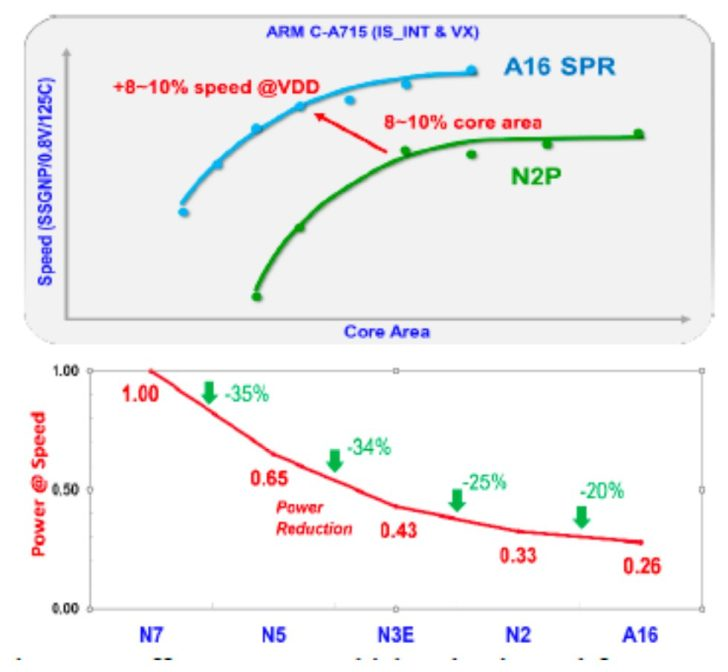

The most important correction to the headline story is this: A16’s official uplift is measured against N2P, not the original base N2 node. TSMC says A16 will provide an 8% to 10% speed improvement at the same power, or a 15% to 20% power reduction at the same speed, alongside up to 1.10x chip density. That makes A16 look less like a simple shrink and more like a performance focused extension of the 2nm family for customers building very demanding AI and HPC silicon.

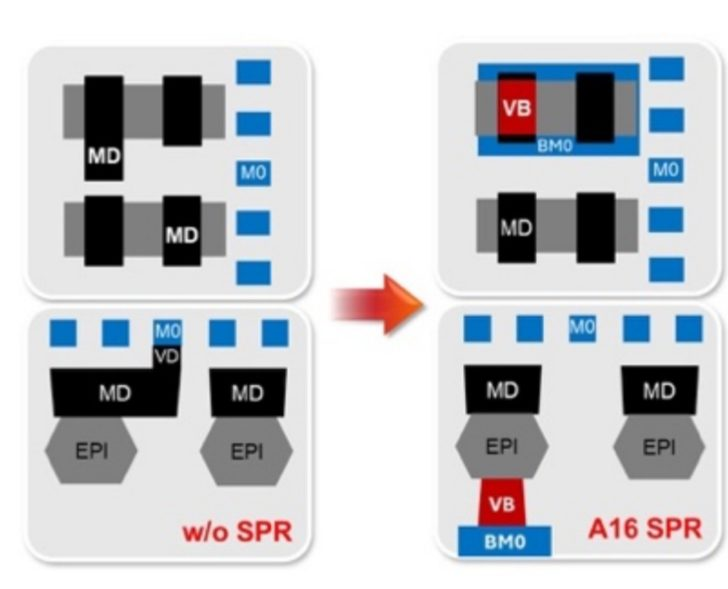

What makes A16 stand out technically is Super Power Rail, TSMC’s backside direct contact power delivery implementation. The company says this approach improves logic density and performance by freeing front side routing resources for signals while also reducing IR drop and improving power delivery efficiency. In practical terms, that means A16 is designed to help large complex compute dies move power more effectively without giving up valuable signal routing space on the front side of the chip.

TSMC is also keeping the production timeline aggressive. The VLSI 2026 materials say mass production for A16 is slated for Q4 2026. That does not mean retail products will arrive immediately, but it does reinforce that A16 is moving from roadmap talk into a real manufacturing window. For most end products, the more realistic expectation is a 2027 wave, especially for premium AI and server class silicon that will need time to move through design, validation, and packaging.

The broader roadmap around A16 is just as interesting. TSMC announced last month that A13 is a direct shrink of A14 with 6% area savings and full backward design rule compatibility with A14, with production planned for 2029. In the same announcement, TSMC also previewed A12 as an A14 platform enhancement that will use Super Power Rail for backside power delivery and is also scheduled for 2029. That tells us A16 is not a one off experiment. It is the first visible step in a wider Angstrom era cadence that branches between client focused and HPC focused designs.

From a competitive standpoint, A16 matters because it shows TSMC is not waiting for rivals to define backside power as the next big manufacturing milestone. Intel has been vocal about PowerVia, and TSMC’s answer is now clear: bring backside power into a node aimed at advanced AI and HPC customers while keeping the nanosheet platform moving forward. The company is effectively telling the market that its next big edge will come not only from transistor scaling, but from smarter power and routing architecture inside the node itself. That is an inference, but it is strongly supported by how TSMC is positioning A16 and A12 around Super Power Rail.

The real business takeaway is that A16 looks built for the exact part of the market that is spending hardest right now. AI accelerators, large compute dies, and bandwidth hungry datacenter parts need stronger power delivery, denser integration, and every possible gain in performance per watt. If TSMC delivers A16 on schedule, it will give hyperscalers and chip designers another premium option right as the competition for leading edge capacity remains intense.

What do you think will matter more for A16, the raw performance uplift, or the fact that backside power is finally becoming a mainstream production feature at TSMC?