Samsung Takes a First Real Step Beyond ARM With a Reported RISC V SSD Controller Move

Samsung may be preparing one of its most meaningful architecture shifts in years, not in smartphones or flagship processors first, but in storage. According to a report from ETNews, Samsung’s upcoming BM9K1 consumer SSD lineup will use an in house controller chip based on the open source RISC V instruction set architecture, marking what the publication describes as Samsung’s first practical commercial move away from ARM based controller designs in this category.

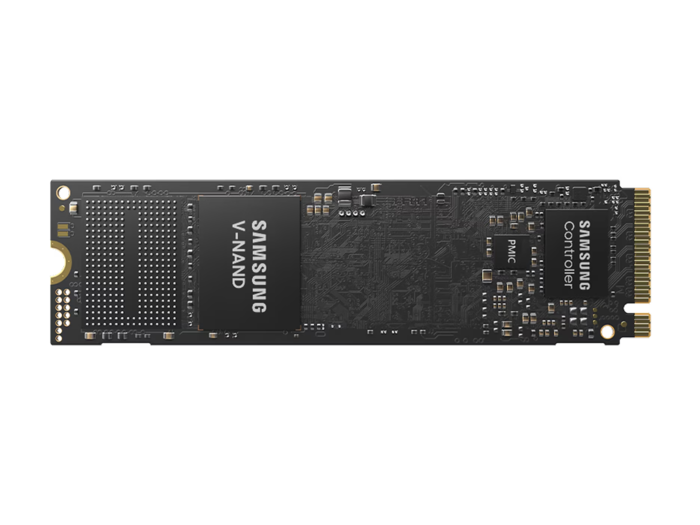

That matters because the SSD controller is not a minor component. It is effectively the operational brain of the drive, responsible for managing data flow between the host system and NAND flash memory while also handling core functions such as error correction, garbage collection, and wear leveling. Up to now, Samsung has reportedly relied on ARM based controller cores in most of its SSD designs, which meant ongoing licensing and royalty costs alongside the strategic limits that come with depending on third party CPU intellectual property. ETNews says Samsung sees the move to RISC V as a way to reduce those licensing burdens, gain more design flexibility, and lower supply chain risk at the same time.

In strategic terms, this is a small but very notable pivot. Samsung is still deeply embedded in ARM’s ecosystem across much of its broader semiconductor portfolio, including its latest Exynos mobile efforts. But storage controllers are a much more practical place to begin experimenting with a different architecture because they are highly specialized, more tightly scoped, and easier to customize around a defined workload. ETNews notes that embedded and storage products offer greater freedom for early architectural testing than more complex product categories, which is why an SSD controller makes sense as Samsung’s first serious commercial RISC V deployment.

Samsung would also not be entering completely uncharted territory. Western Digital said back in 2018 that it was advancing RISC V development and introducing its own SweRV core, with storage and data centric applications forming part of that broader effort. That precedent is important because it shows the SSD and storage side of the chip market has already become one of the more realistic proving grounds for RISC V adoption. Samsung’s reported BM9K1 move therefore looks less like a radical gamble and more like a calculated entry into a space where open ISA designs already have some technical credibility.

The performance angle is also worth watching. ETNews reports that Samsung has added its own custom extensions on top of the open source base and tuned the controller for NAND management, ECC, and the irregular read write patterns associated with AI related workloads. According to the report, Samsung expects the new generation to deliver 1.6 times higher sequential read performance and 23% better energy efficiency versus the previous BM9C1 generation. Those are substantial claimed gains, and if they hold up in market products, Samsung would not just be saving on licensing, it would be using architectural independence to directly improve product competitiveness.

The bigger industry story, however, is what this could lead to next. ETNews points out that Samsung has explored RISC V before in internal projects, including imaging sensor related processors, but those efforts reportedly never moved beyond the demo phase. If the BM9K1 line really becomes Samsung’s first commercialized RISC V design in a mainstream consumer product, it could serve as a foundation for broader adoption later in server SSDs, storage silicon, and potentially even other semiconductor categories. ETNews specifically raises the possibility that Samsung could eventually expand RISC V into additional product groups, including mobile application processors. That does not mean Exynos is suddenly abandoning ARM tomorrow, but it does show why this SSD controller move is more significant than it might first appear.

For now, the most practical takeaway is that Samsung appears to be using storage as its first real escape hatch from ARM dependency in a shipping product class. It is an incremental move, not a full ecosystem break, but it is still a meaningful signal. If the BM9K1 line launches as reported, Samsung will have turned years of RISC V experimentation into an actual product strategy, and that could make this one of the more important quiet semiconductor developments of 2026.

Do you think Samsung’s RISC V SSD controller move is just a cost and flexibility play, or could it be the first visible step toward a much broader architecture shift across its chip business?